Language: English | Size: 3.25 GB | Duration: 9h 45m

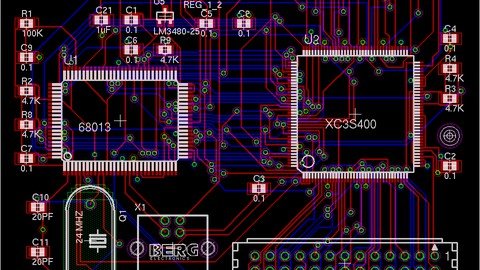

Build your foundation in digital domain by mastering VHDL and become a Digital Design Engineer – Rahsoft RAHDG432

What you’ll learn

Basic Concepts of Digital Electronics

Sequential vs combinational

SR Latch

Flip Flops

PLD Family

FPGA Basics

VHDL Basics

FIFO

ISE Software

Generic

Synchronizing

Test Bench

ISE Simulation

BCD code to Excess-3

Demultiplexer

Hierarchical and External Naming

Description

Description

In RAHDG 432 we’ll Focus on designing different types of digital systems using VHDL language code then we simulate those in the ISE software and at the end we do the implementation. It includes Design and analysis of latches and flip-flops. Number of digital designs have been designed in VHDL language to make you understand them better.

This course describes the different types of design units in VHDL such as entity, architecture, configuration, package and package body. The design and analysis of synchronous state machines. State minimization and introduction to state assignment. Each topic will have many examples which goes over them briefly with different parts. By end of chapter 2 and 4 there will be a quiz for you to test your understanding of that specific chapter.

Core subject of this course is digital design flow. Topics include PLDs, Flip Flops, latches, Digital Design flow, encoder, signals. By end of the course, you should be able to design, simulate, implement, and troubleshoot our VHDL codes using appropriate techniques and test bench.

This course is mostly for academic level Engineering students in different universities around the world.

Since you would be having a lifetime access to this course you would be able to revisit during your career as year passes to refresh your memory.

Instructor

The instructor of this course is Mehrad Nahouri. He has an Associates in Electrical Engineering concentration on digital field and is a lecturer at Rahsoft.

What is the target audience?

This course is for students working in VHDL field.

Undergraduate students

Electrical Engineer

Computer Engineer

Graduate students taking VHDL course

Researchers in VHDL field

Course content

Introduction

Basic Concepts of Digital

Sequential vs combinational

SR Latch

Flip Flops

PLD Family

FPGA

VHDL

FIFO

ISE Software

Generic

Synchronizing

Test Bench

ISE Simulation

BCD code to Excess-3

Demultiplexer

Hierarchical and External Naming

Who this course is for:

Electrical Engineers

Computer Engineers

Electrical Engineering Students

Computer Engineering Students

Who this course is for:

Electrical Engineers

Electrical Engineering Students

Computer Engineers

Computer Engineering Students

Password/解压密码www.tbtos.com

会员内容与购买链接内容一样,升级VIP全部资料免费

评论0